50 milijardi tranzistora na površini veličine nokta povećat će brzinu čipova i smanjiti potrošnju

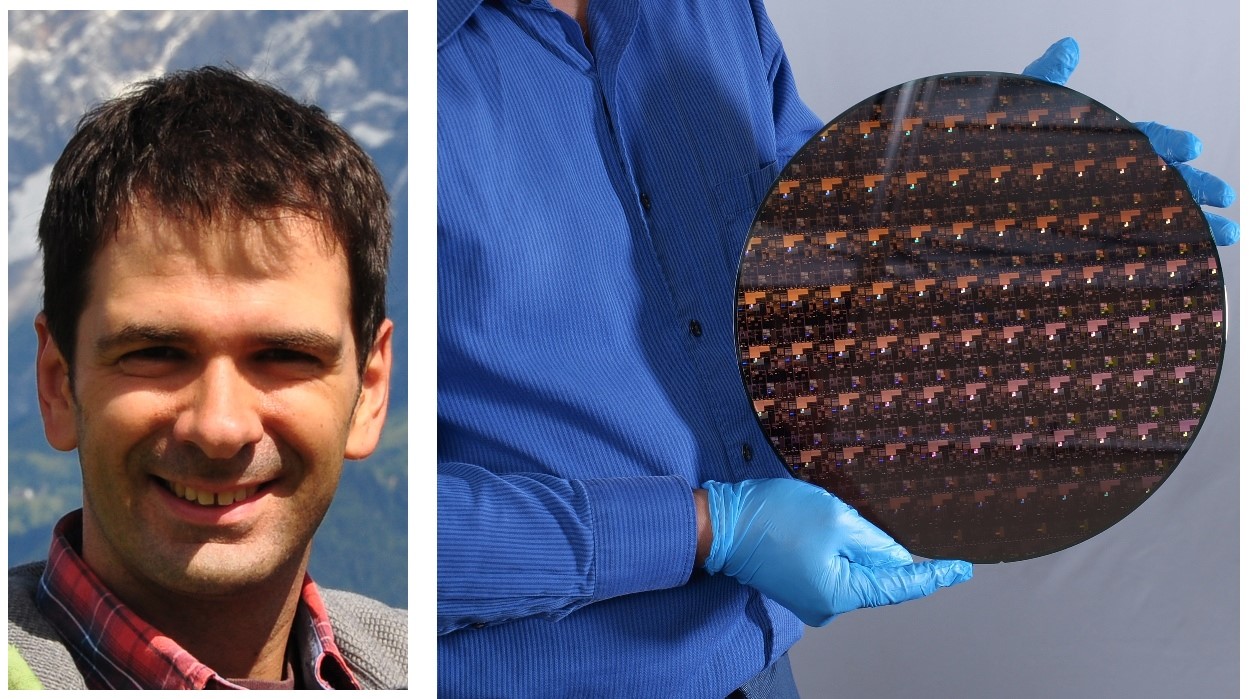

Tomislav Suligoj, redoviti profesor na FER-u i voditelj Laboratorija za mikro i nano elektroniku (MiNEL), komentira najavu IBM-a da će uskoro započeti proizvodnju 2-nanometarskih čipova dramatično poboljšanih performansi

IBM je prošli tjedan predstavio 2-nanometarsku tehnologiju proizvodnje čipova, o čemu smo pisali i na stranicama Buga. Prvi 2-nanometarski čip na svijetu proizveden je u pogonima IBM-a u Albanyju. Time je ova tvrtka otvorila novo poglavlje u proizvodnji poluvodiča koji bi, vjeruju u IBM-u trebali biti daleko efikasniji i s boljim performansama od postojećih.

Dominantna tehnologija

Što to doista znači, na čemu zapravo počiva ova tehnologija i kad je možemo očekivati, objašnjava prof. dr. sc. Tomislav Suligoj, redoviti profesor na FER-u i voditelj Laboratorija za mikro i nano elektroniku (MiNEL) u kojem se istražuju i razvijaju poluvodički elementi i tehnologije, modeliraju i simuliraju nove poluvodičke strukture te projektiraju integrirani sklopovi.

"Riječ je o CMOS tehnologiji (Complementary metal-oxide-semiconductor) na silicijskoj podlozi. To je danas dominantna tehnologija u poluvodičkoj industriji koja pokriva više od 90 posto tržišta", otkriva Suligoj. Baza CMOS tehnologije je MOSFET, tranzistor s efektom polja (Field effect transistor) koji se tradicionalno realizirao na površini silicija i to su bili planarni tranzistori.

Stalno poboljšanje tehnoloških performansi

Otprilike svake dvije godine duljina kanala tranzistora smanjuje se prema Mooreovom zakonu i zbog toga svjedočimo poboljšanju performansi tehnologije. Veća brzina rada i veća gustoća tranzistora po jedinici površine rezultiraju većim kapacitetom memorija, većem broju bitova, itd. S druge strane, smanjivanje duljine kanala tranzistora uzrokuje veće struje curenja, što znači veću potrošnju čipova u stanju mirovanja.

"S obzirom na široku upotrebu mobilnih uređaja koji koriste napajanje baterijama, ovo se nastoji izbjeći kako bi baterije trajale što duže", kaže Suligoj. "Treba imati na umu da se u današnjim čipovima može nalaziti više od 10 milijardi tranzistora i dovoljno je da svaki od njih barem malo curi pa da ukupna struja na čipu bude nedopustivo velika."

Da bi se to spriječilo, prije desetak godina, negdje od 28 nm tehnološkog čvora, umjesto planarnih tranzistora počeli su se kao tijela tranzistora koristiti stupići ili peraje (FinFET) kod kojih se upravljačka elektroda nalazi s dvije strane tijela, ili čak s tri strane u Tri-gate tranzistoru kakav primjerice koristi Intel.

"Kod duljina kanala koje se očekuju u sljedećim godinama, čak i FinFET ima nešto veće struje curenja pa se koriste arhitekture nano-listića (Nanosheet) ili nano-žica (Nanowire) kod kojih upravljačka elektroda u potpunosti obuhvaća tijelo tranzistora sa svih strana i tako dodatno smanjuje struju curenja", upozorava Suligoj.

IBM, TSMC i Samsung

Objavljena IBM-ova tehnologija je jedna od prvih implementacija nano-listića kod kojih svaki tranzistor ima tri listića debljine 5 nm, jedan iznad drugog, kroz koje teku struje. Dimenzija od 2nm predstavlja tehnološki čvor. Tradicionalno, kod planarnih tranzistora, pa čak i kod FinFET-a to je odgovaralo duljini kanala, no današnji kanali su ipak duži od tehnološkog čvora, jer bi u 2 nm duljine kanala stalo tek nekoliko atoma silicija.

"Smatra se da bi duljina kanala IBM-ovog tranzistora bila oko 12 nm", kaže Suligoj. "To je, uz TSMC i Samsung, trenutno jedna od najnaprednijih tehnologija. Pri tome je TSMC ostao pri FinFET strukturi, a Samsung također koristi horizontalne nano-listiće."

Prema objavi IBM-a, ova tehnologija omogućuje procesiranje 50 milijardi tranzistora na "površini veličine nokta", dakle oko 150 kvadratnih milimetara. Očekuju se poboljšanja performansi, prvenstveno brzine, za oko 45% i(li) smanjenje potrošnje za oko 70% u odnosnu na danas komercijalno najnapredniju 7 nm tehnologiju, objašnjava Suligoj.

Ova tehnologija mogla bi postati komercijalno dostupna otprilike kada i TSMC-ova 3 nm tehnologija, dakle za dvije-tri godine.

Očekivano vrijeme života čipova

"Nakon što se demonstriraju pojedini tranzistori, tehnologija mora postići zadovoljavajući prinos. On se definira kao broj čipova koji rade po specifikacijama u odnosu na broj proizvedenih čipova", kaže Suligoj. "To znači da razlika u karakteristikama tranzistora na jednom čipu te od čipa do čipa mora biti minimalna. A to zahtijeva vrlo preciznu kontrolu parametara pojedinih procesnih koraka."

Paralelno se ispituje i pouzdanost tehnologije, odnosno očekivano vrijeme života pojedinih čipova. Do komercijalizacije tehnologije, kompanije će intenzivno raditi na ovim stvarima. A kad se, najvjerojatnije za dvije-tri godine, najnapredniji procesori i memorije pojave na tržištu, oni će se, baš kao i dosad, prvo realizirati u svim vodećim mobilnim, komunikacijskim i računalnim uređajima, najavljuje Suligoj.